ДѓЪ§Он:Intel XeonЁЂLSI SASЪѕвЕгазЈЙЅ

ЛЦСС ЗЂБэгкЃК12Фъ07дТ11Ше 14:23 [зЊди] БШЬиЭј

Жјет2ИіВПЗжЃЌЧЁКУЖМЪЧЯрЖдгкIntel C600ећКЯSASПижЦЦїЕФгХЪЦЃЌгЩгкPCHУЛгаЮЊSAS PHYДюХфзЈгУЕФДІРэЦїЃЌПЩФмЛсЯћКФвЛВПЗжCPUДІРэзЪдД(ЖдXeon E5РДЫЕЕЙЪЧгАЯьВЛДѓ)ЁЃЕБШЛC600зюДѓЕФКУДІОЭЪЧУтЗбЁЃ

ЛиЕНБОЮФПЊЭЗЕФC610аОЦЌзщЃЌIntelЯТвЛДњШдШЛЛсВЩгУЗўЮёЦїCPUЁЂаОЦЌзщКЭИпЖЫЬЈЪНЛњЙВгУЦНЬЈЕФЩшМЦЁЃдк12Gb/s SASНЋвЊПЊЪМВњЦЗЛЏЕФНёЬьРДПДЃЌЮДРДШдШЛЬсЙЉ3Gb/s SASНгПкгаЕуЫЕВЛЙ§ШЅСЫ?ЖјЖдгкзРУцгІгУРДЫЕЃЌаТМгШыЕФUSB 3.0 5Gb/sИпЫйНгПкгжУЛгазуЙЛЕФРэгЩЪЙIntelНЋDMIЕФЫйЖШДгPCIe Gen2ЬсЩ§ЕНPCIe Gen3ЃЌБЯОЙФЧбљвтЮЖзХCPUвЛЖЫвВвЊЖдгІзіГіИФБфЁЃ

БЪепдкБъЬтжаЪЙгУСЫ“ДѓЪ§Он”МИИізжЃЌДѓЪ§ОнЪБДњВЛНівтЮЖзХЗЧНсЙЙЛЏЪ§ОнЕФЭкОђКЭЗжЮіЃЌЛЙгаЖдДцДЂШнСПКЭадФмашЧѓЕФЬсЩ§ЁЃЖјЩСДцКЭSSDПЩвдЫЕЪЧетвЛЪБДњЕФДпЛЏМСЃЌжиаТЖЈвхСЫШЫУЧЖдДцДЂЛљДЁМмЙЙЕФадФмЕФШЯЪЖЁЃНјвЛВНбгЩьЕНЮДРДЛљгкIntel Xeon E5ЦНЬЈЕФДцДЂЯЕЭГЩшМЦЃЌМШШЛФПЧАC600ЯЕСааОЦЌзщЕФSASПижЦЦїУЛгазуЙЛЕФДјПэЃЌЛЙвЊОЙ§SASРЉеЙЦїСЌНгИќЖрЕФЧ§ЖЏЦїЯдШЛВЛКЯЪЪЁЃ

НшгУвЛЮЛвЕФкХѓгбЫЕЙ§ЕФЛАЃК“ШчЙћIntelАб(C600жаЕФ)SASзіЭъЩЦСЫЃЌLSIгжШЅзіЪВУДФи?”БОЮФБъЬтжаЕФ“ЪѕвЕгазЈЙЅ”вВЪЧЭЌбљЕФЕРРэЁЃ

УдЮэгжЦ№ЃК6Gb/s SASПижЦЦїPCIe 3ЩЯааСЌНг?

ЕБЮвУЧПДЕНIntelЮФЕЕжаЯТУцетЖЮЮФзжЪБЃЌОѕЕУЮДРДЫЦКѕШдДцдкБфЪ§ЁЃ

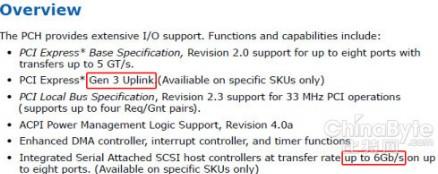

ШчЙћетИізЪСЯжаУшЪіЮоЮѓЕФЛАЃЌC600 PCHжаЕФPCIe UplinkгаПЩФмЛсДяЕНGen3 ХЖ(ЯждкЛЙУЛгаЭЦГі)?СэЭтSASПижЦЦїЕФДЋЪфТЪ“up to 6Gb/s”дйДЮБэУїСЫзюГѕЕФЩшМЦЃЌЕЋЪЧВЛжЊЕРЮДРДЛЙФмЗёжЇГжЕНетвЛЙцИё?

6Gb/s SASЦШЧаашвЊPCIe 3.0Т№?ЕБШЛВЛЪЧЃЌвђЮЊLSIЕквЛДњВњЦЗx8 PCIe 2.0ЕФЗНАИвбОКмГЩЪьСЫЁЃВЛЙ§Intel C600КЭЮДРДЕФC610 PCHЬсЙЉЕФPCIe UplinkжЛЪЧx4ЖјВЛЪЧx8ЃЌЫљвдОЭЯдГіPCIe 3.0ЕФживЊвтвхЃЌЬиБ№ЪЧдк8ЖЫПкЕФХфжУЯТЁЃ