2月24日消息,据韩媒报道,为了获得长江存储技术授权,三星与长江存储签署了3D NAND混合键合专利许可协议!据透露,三星评估认为从第10代NAND设计开始,已经无法再避开长江存储混合键合技术专利!

在SSD NAND 存储芯片市场方面,三星、SK 海力士、铠侠、美光、西部数据等大厂共占据约 91% 的市场份额,其中,三星以35% 左右的份额雄踞第一,与之相比,包括长江存储在内的其他厂商总共占据 9% 左右的市场份额,影响力远不及三星。

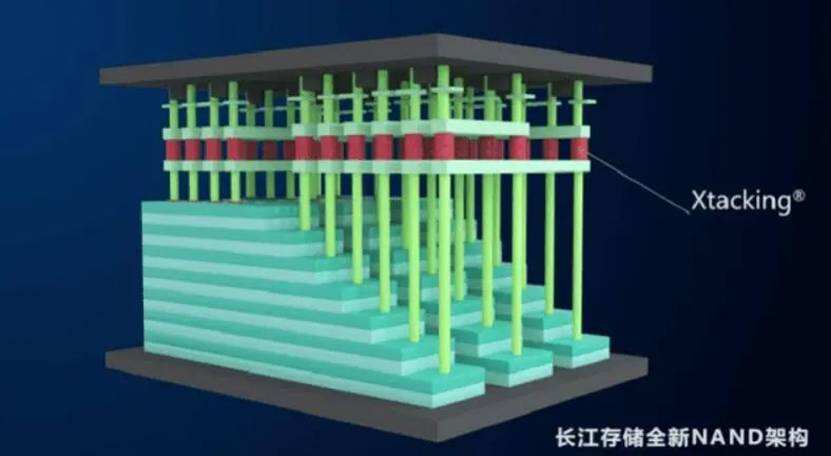

此次三星与长江存储签署3D NAND混合键合专利许可协议,充分说明了一个问题,3D NAND芯片设计开始走向“分离式”架构,也就是在制造工艺上,将存储芯片单元与控制电路设计分开制造,最后通过键合的方式连接在一起,这也就是长江存储3D NAND混合键合专利的核心技术内容。

如果熟悉半导体芯片工艺制造,应该知道CPU处理器芯片早已经历过类似的演变和洗礼,2019 年,AMD 正式初次尝试 Chiplet 封装,将不同工艺节点、CPU 内核及 I/O 规格不同的芯片封装在一起,此后,AMD 在推出的多款产品如 3D V – Cache、Instinct MI300 等中都采用了 Chiplet 技术。

通过采用Chiplet 技术,AMD将CPU计算内核采用更为先进的支撑工艺技术制造,如7nm,3nm;而采用14nm工艺制造技术设计和制造相关的控制电路,然后借助键合技术封装为一个完整的CUP处理器,可以说,借助Chiplet以及台积电的先进工艺制程技术,AMD处理器占据了市场的先机,帮助AMD处理器在竞争中占据了主动。

AMD并不是Chiplet技术的创造者,Chiplet 这一术语是 2006 年由加州大学伯克利分校的 John Wawrzynek 教授在 RAMP 项目中创造的。而 Chiplet 技术的概念可以追溯到上世纪 70 年代的多芯片模组(Multi-Chip Module,MCM)技术,这种技术将多个较小芯片组装在一起形成一个更大的芯片。在 2013 年,Xilinx 就与台积电合作,采用 Chip-on-Wafer-on-Substrate(CoWoS)3D IC 工艺,将大型 FPGA SoC 拆分成了 4 个较小的芯片,算是较早实施 Chiplet 设计的案例。2015 年,Marvell 创始人周秀文博士在 ISSCC2015 上提出 Mochi(Modular Chip,模块化芯片)概念,这也是 Chiplet 的早期雏形。

尽管AMD 不是 Chiplet 技术的创造者,但这并不妨碍其在生产实践中的领先;

与CPU处理器发展类似,但3D NAND追逐的并不是先进的制程工艺技术,而是通过3D,也就是3维,通过堆叠芯片的层数,向空间要效益;在技术路线上,有电荷撷取(Charge Trap)技术和浮栅(Floating gate)技术的区分,前者通过3D锥孔,后者键合与外围控制电路进行连接。三星是前者的代表,长江存储则是后者技术的实践者。

按照预计,三星计划 2025-2026 年推出第十代 3D NAND,采用三重堆叠技术达到 430 层;并计划在 2030 年实现 1000 层,即 V13 代产品,这种堆叠能力让人瞠目,如今,三星开始采用3D NAND混合键合技术,其中的原因耐人寻味。未来,3D NAND是不是会向CPU处理器一样,追逐更加先进的半导体制造工艺技术,不知道有没有这种可能性

无论如何,三星与长江存储合作说明,作为混合键合技术的先行者和实践者,长江存储专利技术可以帮助到三星,站在巨人的肩膀之上也非常符合商业市场的经营逻辑。但是深层次的原因,还有待于进一步观察!