“存储极客”栏目再次与大家见面啦!在这里,只有一位大咖名叫“存储”,它的粉丝我们称为“存储极客”!

存储极客

这是一群存储偏执狂

为存储而生,跟存储死磕

各具独家秘笈

有观点,有碰撞,有干货

从8月18起

做客存储极客栏目

与你分享存储里的那点事儿

前不久,全球闪存峰会(Flash Memory Summit,以下简称FMS)的技术委员会主席Brian Berg在北京演讲时表示,“摩尔定律是一个非常伟大的定律,但是在闪存市场,现在看来闪存技术的发展是可以超过摩尔定律的。”

什么?没听错吧?戈登·摩尔那个伟大的摩尔定律,那个纵贯微处理器乃至整个半导体行业技术发展的摩尔定律,会在闪存技术的发展中,失效?但是显然,当着会议现场1000多位听众,Brian Berg身为全球最大闪存、内存方面会议的技术主席,不会是信口开河,那么,问题显然就转变为了,“为什么闪存技术的发展会超过摩尔定律?”

首先,让我们先回顾一下摩尔定律:在价格不变的前提下,集成电路芯片上所集成的电路的数目,每隔18个月就翻一番。在过去的五十年(摩尔定律是1965年提出的),摩尔定律一直发挥着效用,但是在最近几年,随着制程工艺的进步变得越来越难,认为英特尔等处理器供应商无法继续延续摩尔定律发展的观点甚嚣尘上。但在闪存技术上,却截然相反,持Brian Berg同样观点的人认为:“闪存技术的发展正在打破摩尔定律,这种打破,是超越而不是无法遵从。”

但为什么闪存技术会出现超越摩尔定律的情况呢?众所周知,闪存同样是一种半导体技术,其整体容量和性能发展,应当充分遵从摩尔定律,特别是闪存技术(比如NAND Flash)的制程工艺步进与处理器是类似的:

NAND闪存制程

还不是很突出

2014年市场上的主流制程技术是三星和东芝的19nm以及SK海力士和英特尔/美光的20nm;2015年,市场正逐步过渡到15nm和16nm技术;到2016年第四季度,除东芝将提供13nm左右的制程工艺之外,三星、SK海力士、英特尔/美光将会把支撑维持在14nm制程级别——事实上,英特尔的14nm制程处理器上市已经有很长一段时间了,闪存技术到2016年如果采用14nm制程的话,要比英特尔的微处理器晚了接近3年的时间。

但事实却是,闪存技术的发展,特别是企业级产品的普及速度确实超乎想象的快:如今在不考虑压缩或重复数据删除技术的前提下,以戴尔为例,其全闪存阵列的每GB裸容量已经能够降低到1.5-1.6美元这个区间,也就是说,大约一年的时间,企业级全闪存阵列的价格最多降低了60-70%。

另一方面,我们来看企业级SSD,同样是一年前,业界主流产品的最大容量是3.84TB,现在这一数字是6.4TB,也就是大约提高了一倍,而单盘价格实际上还略微下降;而据三星在今年8月份在FMS上展示的路线图显示,最早今年年底,最迟明年上半年,三星将可以在2.5英寸封装中提供约16TB的容量(15.36TB)。

闪存容量的提高显然是和NAND Flash的单位容量及密度有关的,单颗NAND Flash芯片的容量越高,或者说单位面积上的NAND Flash的容量密度越高,SSD的容量(以2.5英寸封装的SAS、SATA或SFF-8639盘为标准)也就越高。

3D TLC NAND Flash:

这么多前缀,怎么解释?

在闪存技术最开始兴起的那几年,我们最常见到的闪存是SLC和MLC,前者即Single-Level Cell,每NAND Flash Cell上都存储1bit的数据,寿命、性能最好,但也更贵,后者即Multi-Level Cell,即2bit/cell,寿命和性能相比SLC有所下降,但成本大约只是SLC的30%左右。

所谓3D TLC NAND Flash中的TLC,与SLC、MLC所描述的对象是相同的,即Trinary-Level Cell,即3bit/cell,在一个Cell上做到存储3bit的数据是一件相对比较难的事情,成本只是每单元2bit的MLC闪存的约三分之二,速度和寿命表现虽然相比MLC有所下降,但相对传统HDD而言,仍然是天壤之别。

但为什么TLC要比MLC更难实现呢?这就要说下NAND Flash的“存储机制”,或者说是“如何存储数据”:众所周知,计算机存储的数据是二进制,也就是1和0,在半导体上,这实际上可以简单地理解为“有电”“没电”或是“电压高”“电压低”,也就是只要有可以通过电位表达“非黑即白”就可以了。

所以,对NAND Flash写入1,就是控制Control Gate去充电,使得存储的电荷够多,超过阈值Vth,就表示1了,而对于写入0,就是将其放电,电荷减少到小于Vth,就表示0了——在MLC中,其实现机制就是,通过控制内部电荷 的多少,分成多个阈值,从而储存为不同的数据。

试想,在2bit/Cell的MLC中要分为几个阈值?要是3bit/Cell呢?事实上,理论上简单的事情,在实际中就显得比较麻烦了:相比SLC来说,MLC已经需要控制4个状态,即00、01、10、11,TLC就需要控制多达8个状态,显然这是一个非常困难的事情,每Cell的bit数量越多,阈值越多、状态越多,更为重要的是,阈值之间的电压差也就越小(总不能内部搞个几万伏高压吧……),出错的概率自然也就越高。

需要补充的是,业界还是有一些“疯子”是不相信自己做不到任何事情的,某些供应商正在考虑4bit的NAND Flash,从来自NAND Flash生产设备供应商的消息显示,东芝很可能是4bit技术的主要推动者,但就东芝方面的消息表示,“这个东西基本上做出来,很难。”

接下来就要说到3D TLC NAND Flash中的3D,这就涉及到NAND Flash的Die的设计,而在此之前,我们要对NAND Flash的几个主要名词做个解释。

在NAND Flash中,每一个“芯片”分为Die、Plane、Block和Page,这里所说的芯片,即每一个封装好的Chip,Die则是晶圆上的小方块,在一个NAND Flash芯片中,可以封装多个Die,无论工艺、技术有如何不同,Die的概念都是基本相同的。

Plane则是NAND Flash能够根据读、写、擦除等命令进行操作的最小单位,一个Plane里面以矩阵的形式包含了若干个Block,这是NAND Flash的最小擦除单位,其中包含了若干个Page,这是NAND Flash的最小读写单位(其中包含若干个Byte)。

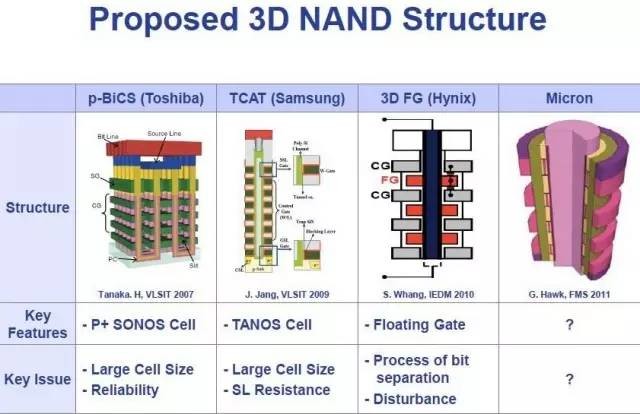

说回到“3D”,为什么叫3D呢?这是因为过去NAND Flash主要是以2D的形式,也就是在平面上排列NAND Flash Cell(存储单元),但三星、东芝等公司后来发现,完全可以采用多层堆叠的方式,于是也就出现了32层乃至48层堆叠的NAND Flash。以三星采用的3D Charge Trap Flash(简称CTF)结构设计的3D TLC V-NAND Flash为例,其精密程度已经迈入到每颗芯片包含853亿个Cell,以3bit/Cell来计算,一共能存储约2560亿bit数据。也就是说,在一个指尖大小的NAND Flash芯片上,可以存储256Gb的数据,而晶圆密度是上一代产品的1.4倍。

东芝NAND Flash业务高层Shigeo Ohshima曾透露,NAND Flash的容量会有“持续的、爆发式的、翻倍的增长”,他认为,2016年,体积不变的情况下(2.5英寸封装)容量可以达到32TB,2017年是64TB,2018年是128TB(历史同期来看,传统HDD的容量增长预测是到2020年20-40TB)。

相比东芝计划开战4bit/Cell的NAND Flash,三星则热衷于“堆积木”,这家公司对当前的32层、48层NAND Flash都不太满意,放言“2、3年内会出现100层以上堆叠的NAND Flash”,不知道到时候东芝心情如何?

说了这么多美丽的远景,看起来NAND Flash市场是光明一片,至少对三星、美光、SK海力士、东芝等供应商来说,摩尔定律基本上不够这些公司通过3bit、4bit、32层、48层等技术来进行追赶的了,但摩尔定律的关键在于:既然是“在价格不变的前提下”。那么技术先进了这么多,密度提高了这么多,成本也自然会下降这么多,那什么时候NAND Flash会出现大规模的降价呢?

熬着不降价?

等到2016年再看!

3、4年前,市场上对NAND Flash的降价可谓是“一往情深”,NAND Flash供应商也好,企业级存储系统的供应商也罢,媒体、分析机构、渠道,都认为“NAND Flash会马上进入快速价格下降通道”,从而快速的取代传统HDD在高端、高性能存储介质层的位置。

换句话说,市场非常相信摩尔定律的“魔力”在NAND Flash市场上也能够发挥如同处理器一样的功效,快速取代过去近三十年发展速度远远追赶不上处理器、内存的传统HDD存储介质,可惜,市场告诉我们:真相永远只有一个,并且这一个永远都是最残酷的那个。

根据市场调查机构的数据,2009年至2014年,NAND Flash市场的每GB价格年均跌幅,只有2009年、2011年和2012年超过了30%,在2010年、2013年和2014年,每GB成本下降都只有15%、18%和27%;在2015年至2016年,这一数字实际上预期也只是维持在25%-30%的水平上,这一降幅,离摩尔定律所说的“每18个月翻(降)一番”,可是远得很!

事实上,这也就是为什么过去3-4年,NAND Flash的出货量一直维持在年均增长40-50%这样一个水平线上的主要原因,那么,为什么价格一直迟迟不能真的遵守摩尔定律呢?

这里面的原因非常多也非常复杂,但总的来说,核心原因有两个:第一,在东芝、三星、SK海力士之间的竞争中,几乎所有的NAND Flash供应商都被卷在了这个漩涡中,制程工艺从20nm、16nm到14nm快速推进,1bit、2bit、3bit的介质不断更新,32层、48层的堆叠快速成型,这些技术上的进步都影响着这些NAND Flash供应商的生产线升级、产品设计生产、供货产业链以及市场推广和渠道费用,有一位三星的内部人士曾经这样认为:“原本3年内要拿出来的产品,被压缩到2年,再压缩到18个月,相当于用两代产品的成本去获取1代产品的收入”,所以在如此巨大的成本压力之下,NAND Flash供应商要承受的压力可想而知。

第二个原因和前一个息息相关,那就是NAND Flash供应商希望能够在闪存市场上持续获得“与性能提升成正比的利润率提升”,就像三星将传统HDD业务出售之后,他们不仅希望高利润能够缓解产品迭代所造成的成本压力,更希望能够从NAND Flash和传统HDD之间巨大的性能差距上获得高额利润,这也是NAND Flash供应商迟迟不愿意降价的主要原因。

从上述的原因说明来看,阻碍NAND Flash价格下降的原因,主要是出在NAND Flash供应商本身,这意味着降价空间实际上是比较大的,根据市场分析机构的预计,各大NAND Flash供应商的成本承受能力,大约在2016年上半年会基本上被充分释放,也就是说,2016年下半年,NAND Flash会迎来一波比较大的价格下降,预计2016年全年的NAND Flash价格下滑能够超过40%,逼近50%。

提前释放降价空间,

须保证性能和可靠性

通过率先引入企业级TLC 3D NAND SSD,戴尔能够提供更具价格竞争力的全闪存阵列,并在维护期内无条件更换故障SSD(不计数据写入量/磨损程度)。这种承诺在显示出技术信心的同时,也让用户更加放心。

不过,对企业级存储系统的用户来说,大可不必等到2016年,前面我们说过,戴尔已经将全闪存阵列的价格推进到每GB物理容量1.66美元(仅供参考,与具体配置有关)。需要指出的一点是,某些存储系统供应商虽然也通过数据缩减技术给出了更好看的数字,但其中一些会影响到性能。而戴尔SC阵列还支持增强型压缩,其最大特点是通过与备受好评的自动分层存储巧妙结合,其压缩动作成为定期执行的后台任务,从而有效避免了对写入性能的影响。同时,在不额外添加专用硬件的情况下,高效压缩算法保证了读性能不下降。

3D NAND在一定程度上改善了TLC的写入寿命,而戴尔SC还能通过独特的自动分层存储技术,在读密集型闪存和写密集型闪存之间做读/写分离,进一步保障经济型企业级闪存的可靠性。只需要加入一个高写入耐久度的SLC/eMLC SSD分层承担所有写入负载,既保障了性能,又使随机/重复的数据IO能够合并优化地导入至TLC SSD,达到了“少花钱,多办事”的目的。

上图来自本月在美国举行的闪存峰会上一场戴尔的演讲《Redefining the Economics of Enterprise Storage》。根据其中的统计数据,在20多个月的服务监测周期内,Tier 2分层中66%的SSD驱动器只有不到0.1 DWPD的写入压力。进一步的说明包括:

1.所有进来的写入被引导至Tier 1,数据只是按需移动;(注:取决于用户实际写入量和Replay快照设置的周期)

2.Tier 2 SSD的规格是每天1次完整写入(1 DWPD);

3.在服务期内,没有驱动器的年平均写入量超过1 DWPD。

从某些方面来说,企业级存储系统的供应商为了抢占市场,从2014年底至今,开展了一轮又一轮的“降价”活动,通过其自身与NAND Flash供应商巨大的议价能力、新技术的快速采用以及软件管理控制能力,提供了比NAND Flash价格下降幅度更大的降价空间。换句话说,2016年下半年的NAND Flash降幅,早就在2015年被企业级存储系统供应商们提前释放了。