DOSTOR存储在线 7月4日国际报道: PCM的原理

相变记忆体在数据记录上有一个简单的基本设计:利用热量来改变硫化物玻璃材料的电介性质。

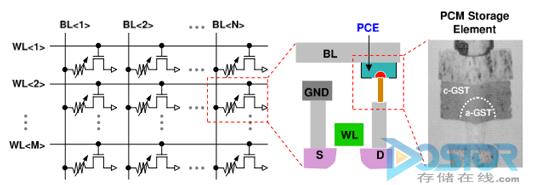

左边,一个示意图显示了相变记忆体单元是如何布置的;右边,放大显示了相变单元(PCE)以及它与电极的接触。

(来源:IBM)

当快速冷却的时候,材料中的分子会保持和加热状态时一样的非结晶态;当慢速冷却的时候,分子则会呈现晶格状态,从而让电流可以更好地通过。通过检测这种电阻性,设备可以计算出有多少个单元在存储,通过加热和有控制的冷却,新的数据可以被写入。

通过多层布置方式,单元的冷却速率可以处在一个中间的水平,这个时候可以利用介于结晶态和非结晶态之间的四种状态。通过四种状态,2比特数据可以存储在每个单元上–二进制下的00、01、10和11–从而将记忆体芯片的存储密度提高一倍,同时减少给定数据存储的成本。

不过这还不够。现在的闪存记忆体可以使用8种状态,这意味着每个单元可以储存3比特数据。

Pozidis表示:“PCM也必须可以储存3比特数据。我相信我们可以做到。”

实际上,他认为PCM可以走得更远。他表示:“通过使用不同材料,我认为我们可以在每个单元上存储4比特数据。”

IBM在一个拥有2.56亿单元的芯片上展示了它的多层单元技术。通过在每个单元上存储2比特数据,它的容量可以达到512MB。Pozidis表示,这个漂移容错技术被应用在了容量更小的2MB版本上。2MB和512MB原型都采用了以前的90纳米制程。

PCM要在成本上取得竞争优势就必须将制程缩小到目前主流的制程。闪存现在的制程是24纳米。Pozidis对此颇有信心。

他表示:“相变记忆体可以采用更小的制程。”

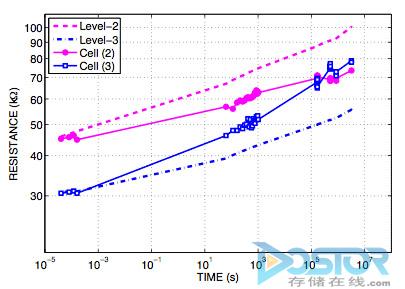

PCM的一个问题就是记录数据用的电阻值会随着时间而发生漂移。上图显示了两个记忆体单元的漂移–每个记忆体可以在四个电阻水平上存储数据。其中一个电阻水平为3的记忆体单元,它的电阻值的升高速度高于蓝色虚线所显示的平均速度,以至于它在某个时间点后高于另一个电阻水平为2的记忆体单元。红色线所显示的电阻值,它的漂移速度则慢于第二层电阻水平记忆体单元的平均速度。

(来源:IBM)

解决漂移问题

在PCM中,不同水平电阻值之间的差异越大越好,不过被称为电阻漂移的问题也会更快出现。因为有漂移,记忆体单元的电阻值会随着时间流逝而发生改变,导致不同电阻水平之间的界限渐渐模糊,并有可能导致数据损坏。这个问题很难解决,因为不同单元的漂移速度也不同。

IBM应对这个问题的方法就是使用一些记忆体单元来记录所谓的代码词而不是实际数据。这个方法,IBM称之为调制编码。它可以让IBM依赖于衡量相对的单元属性而不是单元本身的绝对电阻值。

Pozidis表示:“我们设计了一种调制编码,存储的不是绝对的电阻水平,而是相对顺序。我们知道绝对的电阻水平是会变化的。”

这样做的好处是错误率大大降低,使该技术更加实用化。

这份报告写道:“让我们印象深刻的而是,漂移容错编码所带来的裸错误率也只有10的5次方分之一,也就是10万个记忆体单元中有一个错误。使用简单的低冗余度纠错编码可以将整体的错误率降低到10的15次方分之一,也就是1,000,000,000,000,000个记忆体单元有一个错误。这对于记忆体设备来说足够了。”

Even within the stilted language of academic papers, the excitement comes through.

即使在学术性的语言中,我们也能感觉到作者的兴奋之情。

相关文章:IBM相变记忆体研发迈过两道门槛(上)