面向未来的存储设计,这个话题可能很多人都听到过。不过,对于英特尔来说这句话可能意味着更多:如何从CPU架构考虑存储基础设施?在IDF2010的专题讲座现场,英特尔高级技术营销工程师Aaron Lee向与会者发表了题为《从英特尔处理器(英特尔IOPS)到英特尔架构:面向未来的存储设计》,就这一问题做出了详解。

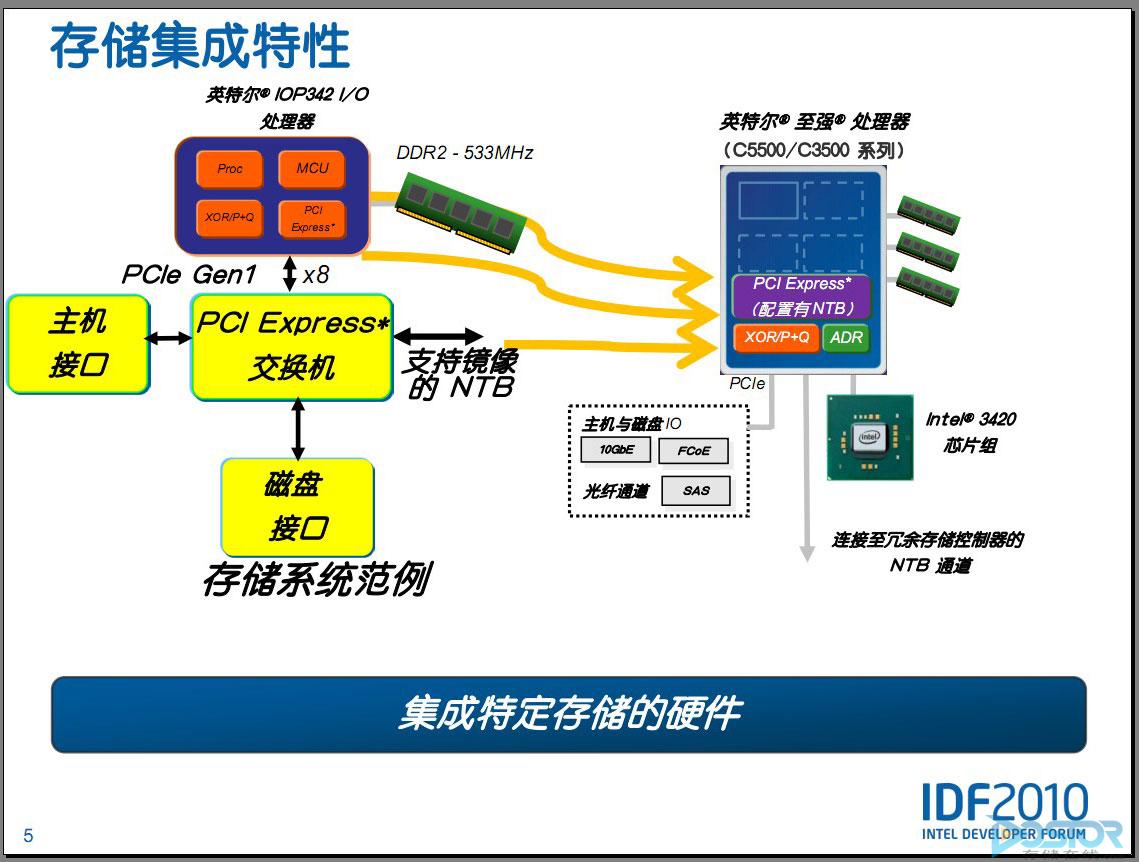

英特尔I/O处理器的基本内容包括嵌入式处理器运行RAID软件、RAID 5和RAID 6的硬件XOR引擎计算奇偶校验、内存控制器单元高速缓存I/O,并在电源发生故障时保护内存、集成PCI Express技术支持外设连接。

Lee表示,英特尔至强处理器C5500/C3500系列专为存储基础设施设计,集成了DMA引擎,可以支持数据移动的DMA以及RAID的增强(XOR/P+Q)。C5500/C3500在iSCSI处理/测试数据方面采用了CRC-32生成/校验,同其也支持伽罗瓦域乘法(Galois Field Multiply)和RAID6的XOR操作。他表示,这两款产品在DMA传输上的速率能够达到1MB。

在XOR/DMA方面,C5500/C3500通过软件来创建描述源/目标操作的描述符"链条"。包括描述符链中的每个部分可处理不同的操作。

"异步 DRAM 刷新(ADR)"是C5500/C3500保护DRAM中关键数据的一种方法。其工作原理是,当电源故障引发外部针脚时,内部"ADR 缓冲器"冲刷至 DRAM,内存被置于"自我刷新"模式。内存则由电池供电,以保存内容。不过,Lee表示,ADR技术不能冲刷或保护处理器高速缓存,这也是一种有的放矢的做法。

Lee同时表示,采用ADR技术也需要考虑一些硬件考虑因素。这包括GPIOs/CPLD 用于记录BIOS的ADR事件以及早期的 A/C 电源故障检测、ADR进入依赖于剩余的DC电量等等。其保存时间依赖于电池和内存容量,最终目的是达到非节流DDR3条件下约20-50uS的保存时间。

在软件方面,实现ADR同样有一些考虑因素,比如说内存的划分、同步以及恢复处理等等。用户在操作中要注意不要擦除 DIMM中的数据。

C5500/C3500针对于存储的专门性设计还包括"非透明桥(NTB)"。其支持通过PCI Express* 的冗余,"窗口"可面向远程控制器内存,在4或8条通道下即可配置为 NTB。

在两个CPU之间的数据传输并非直接进行,而正是要通过NTB来连接。具体流程见下图。

Lee总结了C5500/C3500 架构的演进,包括集成PCI Express Gen II和存储特性、架构可以纵向扩展,可提供多种特性和性能选择,满足所有方面的需求、外部英特尔 QPI连接支持额外的PCIe I/O 扩展、更高的内存带宽带来更卓越的性能和可扩展性以及更大的灵活性,根据特定使用情况使用内部"非内核"资源。英特尔同时提供广泛的产品型号,满足空间和散热受限环境的需求,如存储桥接坞(SBB)(见下图)。

最后,Lee表示,C5500/C3500的几点优势:

可以根据使用模式,灵活分配"非内核资源""BIOS 配置"

持续的系统带宽依赖于读/写比、QPI 协议开销和IIO 请求率

硬件 RAID-6 流镜像写入性能预测可用于架构权衡

在广泛的企业工作负载中,延迟/带宽性能平稳