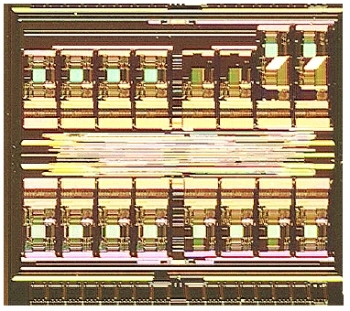

三星:试制成功64Kbit MRAM

图1:试制的64Kbit MRAM(照片提供:韩国三星电子)

一家对手公司的技术人员出席了该公司的报告会后感叹道:“没有什么特别让人吃惊的新观点。然而尽管看上去很普通,但这倒是三星一贯的作法――通过完整的数据来说明其他任何一家公司都没有想到过要去证明的东西。它擅长的这种手段以前就曾利用NAND型闪存EEPROM等产品展示过。可以看出三星正在大力推进MRAM的开发”。

MRAM所面临的技术课题之一是MR比非常低,只有20%~40%左右。而且这个值还只是TMR元件单体的数字,实际上,在作为存储芯片使用的条件下还要更低。比如,MR比不仅会由于施加TMR元件工作所需的偏压而降低,而且单元晶体管的薄膜电阻越高,MR比就会越低。此次三星分别提出了解决这两个问题的方案。对于前一个问题,提出了新的参考单元的电路结构,即使由于施加偏压造成了MR比的降低,也能够正确地读取数据。通过在参考单元中并行连接低电阻状态所用的基本元件和高电阻状态所用的基本元件,就能够向读出放大器提供正确的参考单元信号(高电阻状态和低电阻状态的正中间值)。由于以前的参考单元是直列连接输出低电阻状态的基本元件和输出高电阻状态的基本元件,因此很难控制参考单元信号。对于后一个问题,为了降低薄膜电阻,一方面在单元晶体管的源极、漏极和栅极中采用钴硅化物,同时将栅极绝缘膜的物理膜厚度降低到3.5nm。可以说使用了接近逻辑晶体管规格的单元晶体管。

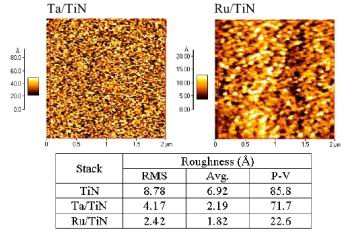

在TMR元件中层叠膜厚度仅为数nm的薄膜的MRAM中,加工的不稳定性也是造成成品率下降的重要原因。其原因比如,隧道势垒层(也称绝缘层,Al2O3)的膜厚度只要改变0.1nm,电阻值就会在数倍范围内变化。三星此次报告说,通过在TMR元件的下部电极(TiN)和引脚层之间将钌用作缓冲层,就能够形成表面粗糙度非常低的平坦衬底(图2)。所制作的下部电极部位的表面粗糙度(平均值)方面,不使用缓冲层时非常大,达到了0.692nm,而在缓冲层中使用钽时为0.219nm,使用钌时却可以将表面粗糙度控制在0.182nm(图3)。

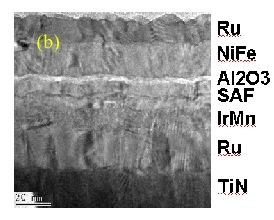

此外,如何制造加工损伤较小的TMR元件,对于MRAM来说也是一个很大的课题。由于对TMR元件的层积膜进行等离子蚀刻时,产生的附属物会附着在Al2O3上,因此隧道势垒层就会失去绝缘性。三星此次通过使用被覆氧化膜,分两个阶段对TMR元件进行蚀刻,从而解决了这个问题。

通过采用以上技术,在试制芯片中所用的90%以上的存储单元,实际MR比达到了30%以上。

图2:如果在缓冲层中使用钌,就能够形成平坦的衬底(照片提供:韩国三星电子)

图3:TMR元件的TEM照片。形成了膜厚度为1.4nm的Al2O 3层(照片提供:韩国三星电子)